# 目 录

## 摘要

前言 ..... 2

## 第一章 数模转换器简介

§ 1.1 DAC 基本原理 ..... 3

§ 1.2 几种不同结构 DAC 的比较 ..... 5

§ 1.3 研究这种新型结构的理由 ..... 6

## 第二章 具体实现原理

§ 2.1 基本结构 ..... 8

§ 2.2 改进方法 ..... 9

## 第三章 设计与仿真结果

§ 3.1 基本单元的设计与结果 ..... 12

§ 3.2 10 位 DAC 的核心设计与结果 ..... 17

## 第四章 设计讨论

§ 4.1 在实现高速过程中的问题 ..... 21

§ 4.2 非理想效应对转换精度的影响 ..... 24

§ 4.3 对电容不匹配的改进 ..... 24

§ 4.4 不足与计划 ..... 26

结束语 ..... 27

参考文献 ..... 28

致谢 ..... 29

## 前 言

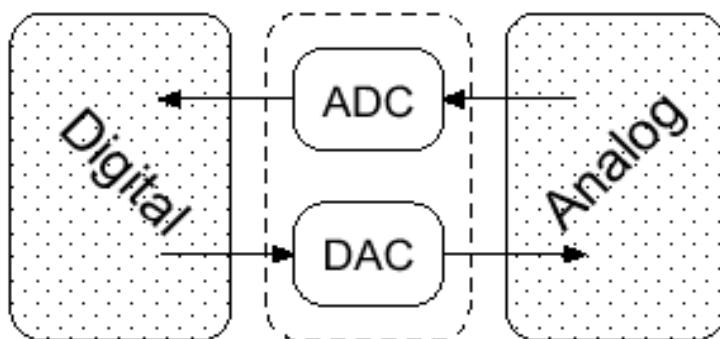

我选择的论文主题是关于数模转换方面的 ,之所以选择这个方向是由于在数字和模拟领域的接口研究中 ,数模转换器 DAC 和模数转换器 ADC 的应用不仅局限于听觉通路的如麦克风和扩音器 ,视觉通路的如照相机和其他一些显示设备 ,而且在有线或无线通道数据传输中也很重要的用途。典型的如数据信号依据某种机制被调制到载波上 ,和载波一起在有线或无线的通道中传输 ,接收器接收到信号再进行解调 ,可根据应用和可行性的不同在数字或模拟领域中解调 ,其应用之广泛可见一斑。

随着近年来对高速通信的需求和对英特网、移动终端应用的飞速增长,许多相应的技术 ,如 DSL , GSM , EDGE , UMTS, WCDMA, GPRS 等就需要大幅度的改进 ,线性度和低功耗是限制这些技术发展的两个大障碍 ,其中的一个瓶颈问题就是数据转换,以 DAC 为例 ,到目前为止 ,对他有影响的因素还有很多 ,如噪声、失配、寄生、延迟等等 ,解决了这些问题也就大大推进了技术和应用领域的发展。

我所研究的新型结构是向传统的电流型 DAC 在高速数模转换领域中所占的垄断地位发起挑战 ,抖动是电流型结构在高频下的症结所在. 而此结构却能在没有抖动 ,又无附加电路和特殊工艺的条件下实现高速度、高精度和低功耗, 所以今天来研究他也就显得格外有意义。

# 第一章 数模转换器简介

## 1. DAC 基本原理

DAC 是为了实现数字和模拟器件的连接在他们的接口上放置的把数字信号转换成模拟信号的器件，其输出端的模拟信号就代表输入端的数字信号。

按其原理划分，DAC 可分为 Nyquist 型和过采样型。Nyquist 型转换器按其结构又可大致分为：电阻分压型、R-2R 称重型、电荷分配型和电流驱动型，一般根据不同的应用，从速度、精度、功耗、主要限制因素、复杂度和芯片面积等多方面入手，综合考虑，选择一个恰当的结构。

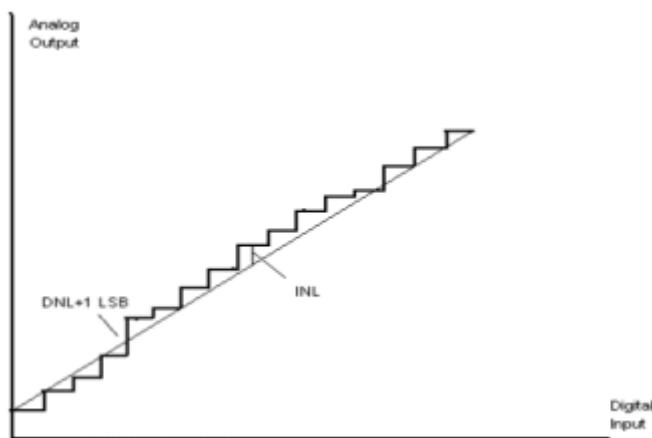

数字量的最低位所表示的模拟量称为 LSB (least significant bit) eg. 10bit, 00000 00001 的理想输出就是这个单位量，数字输入每加 1 模拟输出就会增加一个 LSB，所以输入输出曲线图如台阶状：(如图 1.1)

图 1.1 DAC 输入输出曲线图及部分静态参数

但由于不理想状况的存在，使得输出并不能完完全全代表输入，总会有一些误差，包括幅度上的和时间上的，每一个台阶的高度也不尽相同，有高有低，故而引入静态和动态误差参数来衡量其性能的好坏。

静态参数和信号无关，低频时占主导：(如图 1.1)

DNL (differential nonlinearity) --- 相邻数值输入所得输出的最大差值与 LSB 的差。

INL (integral nonlinearity) --- 实际的 D/A 曲线与通过始末两点的直线的最大距离。

Offset --- 在 D/A 曲线上穿过始末两点的直线与垂直轴的截距。

Gain-error --- 始末两点连线的斜率与理想值之间的差距。

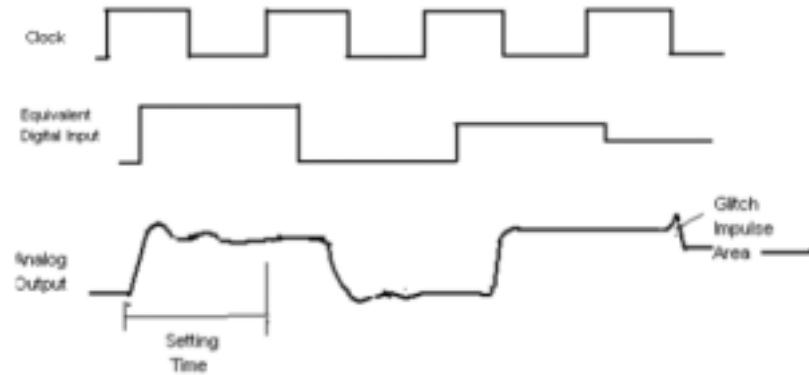

动态参数和信号有关，高频时占主导地位：

Setting time---在最终值的一个特定的误差范围内，输出经历满幅转换所需要的时间。

Glitch impulse area---输入信号变化以后在输出端出现的抖动下的最大面积，也被称为抖动能能量。(如图 1.2)

图 1.2 DAC 部分动态参数

Latency---从输入变化到输出在一个特定的误差范围内建立所需要的总时间。

SNR(signal -to-noise ratio)---当输入为正选信号时，输出端的信号功率与噪声功率的比值。

SNDR(signal -to-noise-and-distortion ratio)----输入为正选信号时，输出端的信号功率与总的噪声和失真功率的比值。

输入端的数字信号可以用不同的编码方式，常用的有 Decimal , Binary , Thermometer 和 1-of-n, (如表\*) 其中 Binary 和 1-of-n 更为常用，且能用较简单的方法进行转换。

表 \*

| Decimal     | 0  | 1  | 2  | 3  |

|-------------|----|----|----|----|

| Binary      | 00 | 01 | 10 | 11 |

| Thermometer | 0  | 0  | 0  | 0  |

|             | 0  | 0  | 0  | 1  |

|             | 0  | 0  | 1  | 1  |

|             | 0  | 1  | 1  | 1  |

| 1-of-n      | 0  | 0  | 0  | 0  |

|             | 0  | 0  | 0  | 1  |

|             | 0  | 0  | 1  | 0  |

|             | 0  | 1  | 0  | 0  |

## 2. 几种不同结构 DAC 的比较

三种不同类型的 DAC 分别以下述的结构实现，注意此处只是给出了一大致的示意，具体的应用还要进行一些细节的改进。

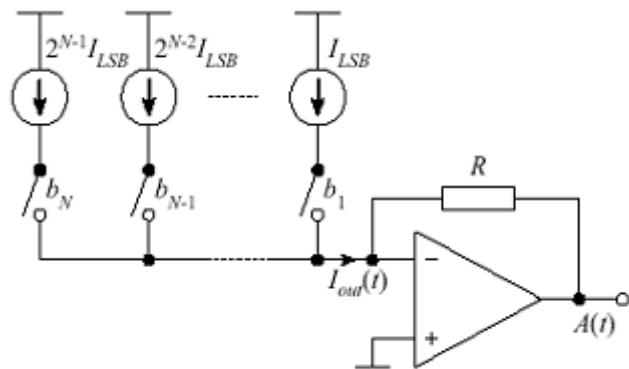

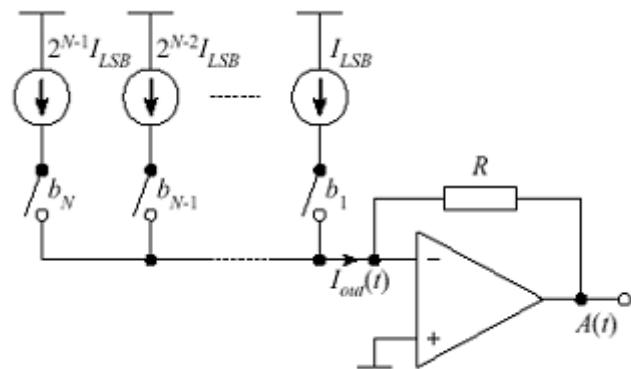

**电流型：**(二进制权重，如图 1.3)

图 1.3 电流型 DAC

其优点是当精度小于 10 位时能将面积做得很小，速度不受放大器带宽和较大 RC 延迟的限制，可达到很高的速度，由于所有的电流都直接流向输出端，所以能量的使用效率很高，且容易实现。缺点是对器件不匹配性的敏感和有限的电流源输出阻抗。适合高速宽带的要求。

**电容型：**(此处指的是传统的二进制电容网络，和本文重点论述的电容型结构不同，如图 1.4)

图 1.4 电容型 DAC

最高位的电容  $C_N$  是最低位电容  $C_1$  的  $2^{N-1}$  倍。优点是功耗较小，匹配精度比电阻高。主要的限制因素是电容的不匹配，开关的导通电阻，较大 RC 延迟以及放大器有限带宽对 DAC 速度的影响。适用于中宽带高精度。

**电阻型 :**( 如图 1.5 )

图 1.5 电阻型 DAC

这是一个 R-2R 阶梯网络型的转换器。其优点在于能实现很好的线性度，由于所有的电流源都是等值的，我们可以用特殊的附加技术使他们间误差较小，与电阻分压相比其结构简单得多。缺点是电阻总是非线性的，还包含着和信号有关的寄生电容，要做到完全匹配较难。

所有这些结构类型的 DAC 都可以用一个公式来描述他们的转换关系：

$$A_{out} = \sum_{m=1}^M w_m \cdot b_m$$

$A_{out}$  指模拟输出量，可以是电压、电流或电荷； $b_m$  指第  $m$  位的输入值； $w_m$  指  $b_m$  相应位的权重。

我们知道线性度是 DAC 的一个基本要求，影响线性度的至关重要的因素是元件的不匹配，所以这里将其特别列出加以考虑。各种结构类型的 D/A 都有不匹配的情况，但引起的原因各不相同：

a. 电流型： 电流源偏差，不匹配

限定的电流源输出阻抗

负载电阻对电压的依赖性

b. 电容型：电容间的偏差，不匹配

电容非线性

输出开关结电容非线性

c. 电阻型： 各电阻不匹配，包括  $|$ ,  $w$  等参数

### 3. 研究这种新型结构的理由

首先对此结构作一个简单的介绍，下一章将进行详细地叙述。他用  $4n+2$  个 MOS 管开关串联  $n$  个等值电容，三相时钟控制运行，每一位第一步执行预充电，第二步和前一位电荷重

分配，第三步和后一位电荷重分配，注意必须在接到前一位结果以后才能和后一位分享，从 LSB 起，转换分配的结果一位一位向后传，直到  $n_{bit}$  转换结果在最后一位电容上出现为止。比起其他结构 DAC，他有很多优势：

- 1) 由于电容网络不消耗直流功耗，所以电容型转换器的功耗很低。

- 2) 电容可达到比电阻更高的匹配精度，电容型 DAC 的分辨率可做得更高。电流、电阻和传统的二进制电容网络 DAC，这些电路的器件数量、电路规模会随着输入位数的增加成指数上升，一个高精度的 D/A 就需要很大的芯片 面积和昂贵的额外电路。而此结构增加一位输入，电容只增加一个，器件随精度线性上升，并非呈指数变化，因而可获得较小的芯片面积。

- 3) 二进制电容网络 DAC 最高位的电容是最低位电容的  $2^{N-1}$  倍，如此大的电容首先严重影响了转换速度，其次占用较大的芯片面积，而此结构所有的电容都是等值的，不存在大电容，改善速度性能。减小芯片面积。虽然匹配仍是一个主要难点，但相同电容间的匹配比呈指数增加的电容间的匹配要容易实现。

- 4) 再用流水线型结构，更能使速度大幅度提高，弥补了电阻电容结构 RC 延迟时间较大和速度受放大器带宽限制的缺陷。

- 5) 电流型是实现高速 D/A 转换的常用方法，但存在抖动(glitch)是他在高频时的最大弱点，用此结构可实现无抖动的高速 CMOS 数模转换器。

综上所述，我们研究的这种新型 DAC 可以在不是很高的时钟频率，无需特殊工艺及额外电路的条件下，实现高速度、高精度和低功耗，这是相对于过去的电阻、电流、电容型 DAC 的决定性优势。

## 第二章 具体实现原理

本文要重点描述的基于开关电容技术的流水线型 CMOS 数模转换器是用 MOS 管作开关连接的等值电容阵列，对  $nbit$  转换，需  $n+1$  个等值电容和  $4n+2$  个开关，以另一种时钟形式，从低位向高位进行转换，在最后与最高位对应的电容上所得到的模拟电压值即转换结果。具体结构如下述：

### 1. 基本结构

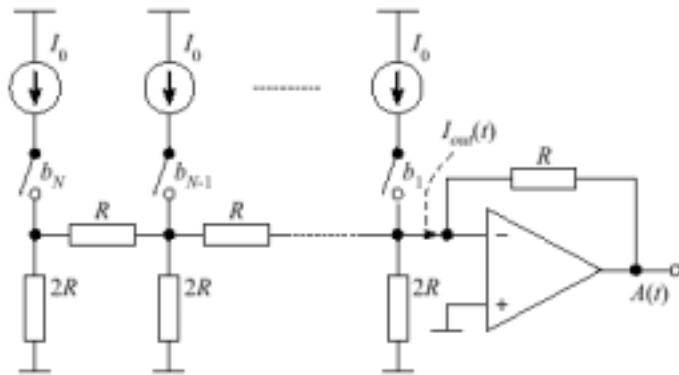

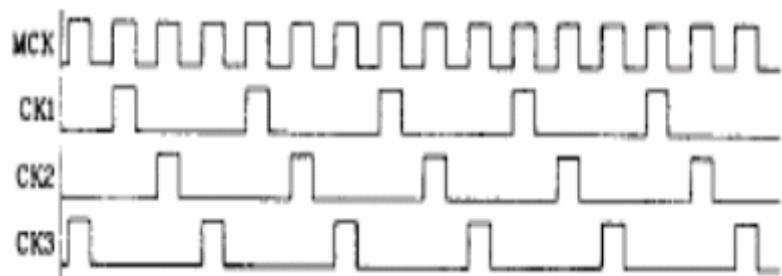

先介绍时钟形式，一个 clock cycle 中有 3 个不交叠的相位， $\phi_1, \phi_2, \phi_3$ ，cycle 一个接一个，即 3 个 phases 按序交替出现。 $b_i^k$  中  $k$  表示第  $k$  个 clock cycle， $i$  表示第  $i$  位输入值， $b_1^k$  即 LSB，每一个时钟相位的延迟时间为  $T$ ：(如图 2.1)

图 2.1 时钟相位

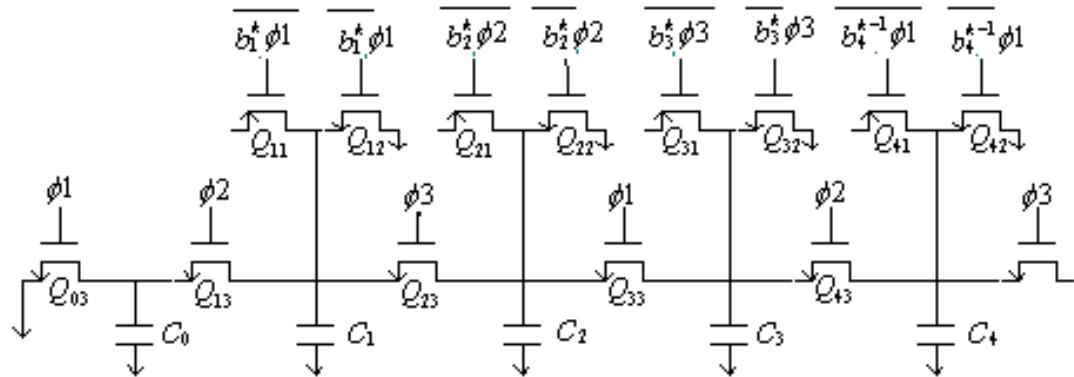

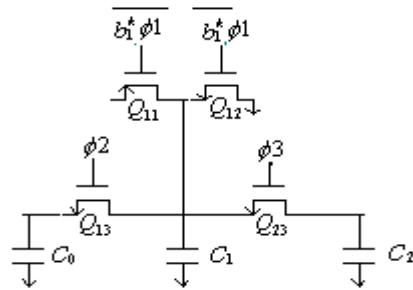

电路结构如图：(以  $n=3$  为例，如图 2.2)

图 2.2 电路结构原理图

电路是这样运行的：

第一步：当  $\phi_1 = 1$ ，电容  $C_1$  预充电，若  $b_1^k = 1$ ，则 MOS 管  $Q_{11}$  闭合， $C_1$  预充电至  $V_r$ ；反之，若  $b_1^k = 0$ ，则  $Q_{12}$  闭合， $C_1$  预充电至 0。（注意  $Q_{11}$  是 PMOS 器件， $Q_{12}$  是 NMOS 器件）同时， $C_0$  通过  $Q_{02}$  放电至地。

第二步： 1 变低， $Q_{02}$  和  $Q_{11}$ (or  $Q_{12}$ ) 不导通了，此时  $C_0$  和  $C_1$  上的电压分别为 0 和  $V_r b_1^k$ 。紧接着 2 变高， $Q_{13}$  导通，电容  $C_1$  和  $C_0$  上的电荷将被重新分配，同时  $C_2$  将被预充电，若  $b_2^k=1$  通过  $Q_{21}$  充至  $V_r$ ，若  $b_2^k=0$  通过  $Q_{22}$  充至地，此过程和  $C_1$  预充电时一样。

第三步： 2 变低， $C_0$  和  $C_1$  上的电压已被重新调整至  $V_r b_1^k / 2$ ， $C_2$  上的电压为  $V_r b_2^k$ 。当 3 来临时， $Q_{23}$  闭合， $C_1$  和  $C_2$  上电荷重新分配， $C_3$  被预充电。

第四步： 3 下降， $C_1$ ， $C_2$  上的电压为  $(b_2^k + b_1^k / 2) V_r / 2$ ， $C_3$  上为  $V_r b_3^k$ 。

第五步：又一 clock cycle，当此 cycle 的 1 结束时， $C_3$  上的电压为  $(b_3^k + b_2^k / 2 + b_1^k / 4) V_r / 2$ ，三位转换结束。

所以在第二个 clock cycle 的 1 结束时，和输入数字量对应的模拟输出结果就可在  $C_3$  上得到。特别值得一提的是每位在和前一位电荷分配时，其后位必然在预充电，这样此步完成后就恰好在下一位执行类似的操作，以达到运行上的同步和高效。

由此可见，每一位输入对应一个电容，加上  $C_0$ ， $n$  位输入所需的电容为  $n+1$  个，一个时钟相位 的周期为  $T$ ， $n$  位输入将在第  $n+1$  个  $T$  变低时在最高位对应的电容上出现转换结果，若再计入将结果输出所需的一个时钟周期，则  $n$  位 DAC 从输入到输出所需的时间为  $(n+2)T$ 。总之，此电路是通过从左至右，即从 LSB 到 MSB，等值电容阵列的电荷重新分配来实现转换功能的。

## 2. 改进方法

- 1) 因为不匹配、噪声等等必然或偶然因素，经过  $n$  阶转换，电路肯定会产生失调，即便没有输入也会有输出产生，用差分电路能够降低失调，减小误差。

- 2) 输入数据每 3 位作为一个 digital word，如  $b_1 b_2 b_3, b_4 b_5 b_6, b_7 b_8 b_9, b_{10}$  这样划分，由于 1 2 3 按序交替作用，所以每个 word 里 3 个输入值并不能同时充到相应的电容上去，只能等次位的 到来时才能作用。另外，虽然各个 word 同时输入对最后的结果并无影响，但后几个 word 却是重复工作，例如：在前 3 位的转换结果还没有到达  $C_3$  上时， $b_4 b_5 b_6, b_7 b_8 b_9, b_{10}$  的转换是毫无意义的，每一位都要在前一位的结果得出后才能发挥作用，之所以同时输入对结果无影响是因为转换是周期性的， $b_4$  在第一和第二个 clock cycle 来临时的运作完全一致，第二个 cycle 时的输入是有效的，才和  $C_3$  上的结果均分，传给  $b_5$ ，第一个 cycle 时输入只是空做， $b_5, b_6, b_7, b_8, b_9, b_{10}$  也有类似情况，这样重复的无效运行既浪费了时间，降低了速度，也无端增加了很多功耗，基于以上分析，想

到用流水线操作，可以很好地解决这些问题，大大提高速度，且最有效地利用了此结构。

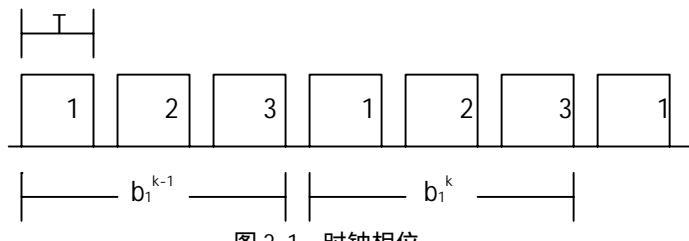

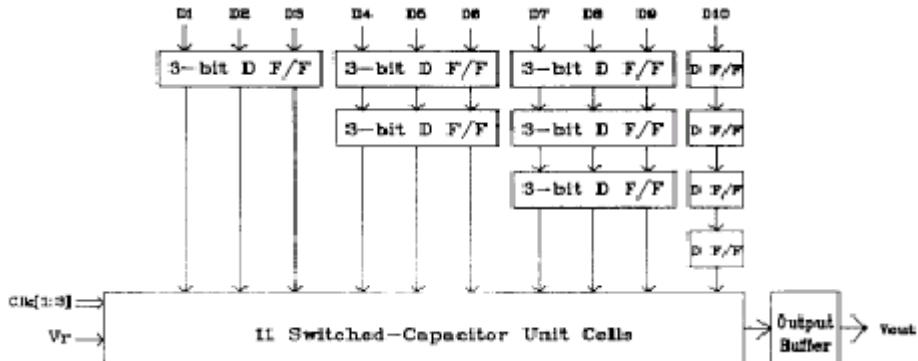

改进的流水线结构：(如图 2.3 )

图 2.3 流水线结构图

图中 D F/F 是由 D 触发器构成的移位寄存器；Clk(1:3)是三相时钟；

11 Switched-Capacitor Unit Cells 就是上述的基本结构；V<sub>r</sub>是参考电压源。

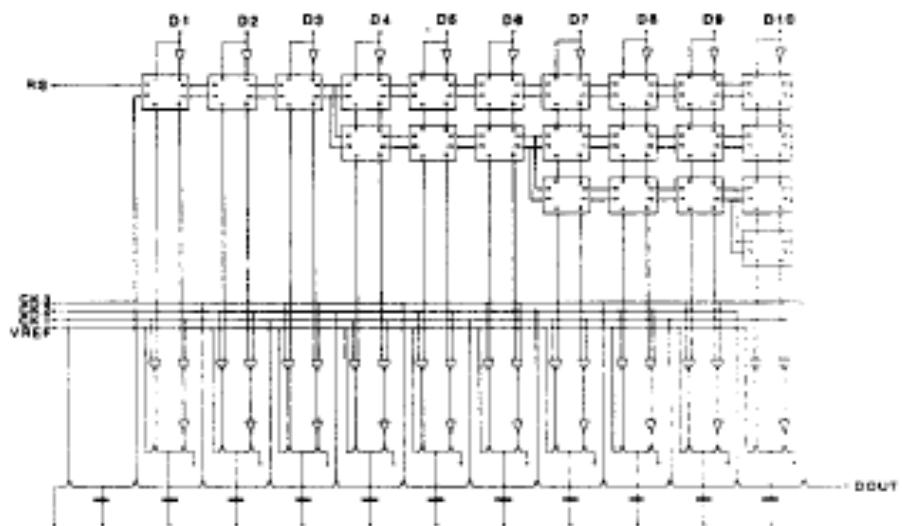

按每 3 位一个 digital word 分批输入数字输入端，从低位到高位通过移位寄存器来实现，第一个 clock cycle 时输入  $b_1 b_2 b_3$ ，应于电容网络的  $C_1 C_2 C_3$ ，进行转换， $b_4 b_5 b_6$ ,  $b_7 b_8 b_9$ ,  $b_{10}$  存放在寄存器里，经过 1 2 3 一个 clock cycle，前三位的 转换已完成了大半，又一个 cycle 来临时， $b_4 b_5 b_6$  从寄存器出，输入到开关电容网络的第 4, 5, 6 位，此 1 结束时，前三位的转换完成。 $b_4$  的预充电也恰好完成，这样  $C_3$  和  $C_4$  上的电荷重新分配，将结果又向前推进了一位，此时  $b_7 b_8 b_9$ ,  $b_{10}$  仍在寄存器里，第三个 cycle 到后， $b_7 b_8 b_9$  输入，以后的过程同前，数据的延缓输入就是这样实现的。在第二个 clock cycle 到来， $b_4$  充电时，电容网络的前 3 位接受下一个 10bit 数据的  $b_1 b_2 b_3$ ，和数据一的  $b_4 b_5 b_6$  同时进行转换，第三个 clock cycle 时。数据一的占据 7, 8, 9 位，数据二占据 4, 5, 6 位，数据三占据 1, 2, 3 位，依此类推。如此，在输出端每经过一个 clock cycle，即 3T，就会得到一个输出结果，比起原来转换完一个再开始下一个， $(10+2)T$  才有一个输出要快得多。这就是流水线型的结构。(具体实现电路和时钟如图 2.4 和图 2.5)

是否使用流水线结构的不同在于：若不使用，则单次转换时间较短，需额外的电路进行转换增益和失调的匹配；若使用，则具有较简单的电路逻辑，较少的面积和器件数量，无需对转换增益和失调匹配。

图 2.4 流水线结构具体实现电路

图 2.5 时钟

## 第三章 设计与仿真结果

从第三章分析看，这种新型结构的 DAC 就是建立在开关电容原理的基础上，通过 n 个相似的电荷分配单元串联而成的。所以首先对一个基本单元进行研究就是本次设计的关键所在。依据一个成熟的单元，把 10bit 串联起来，加上相应的时钟扩展，就能实现此结构 DAC 的核心设计。

### 1. 基本单元的设计与结果

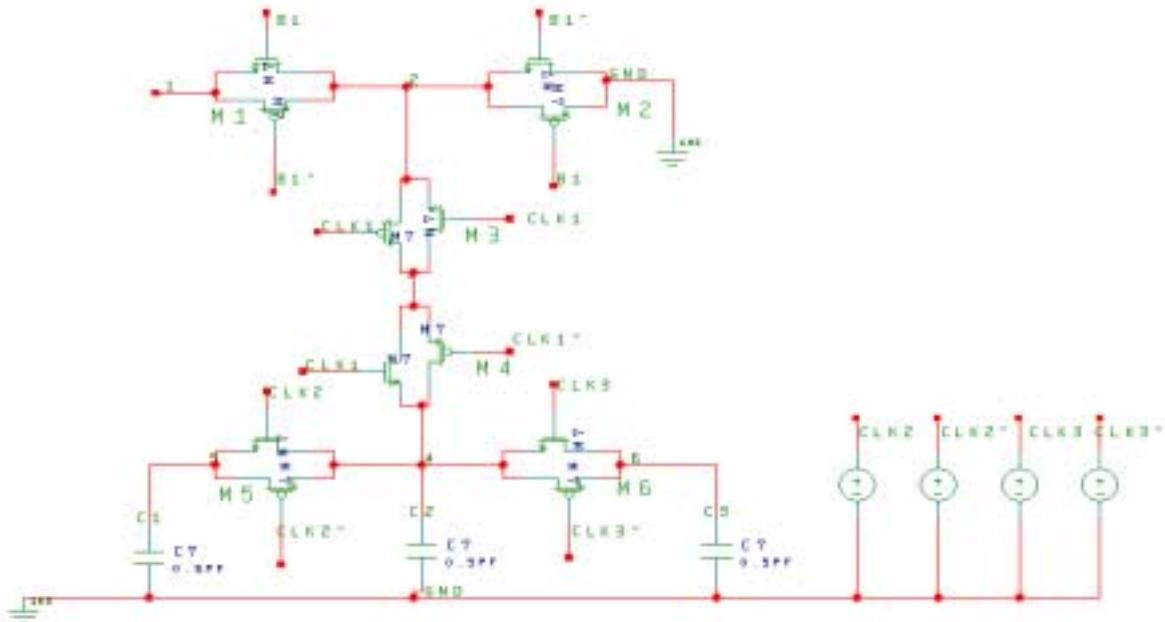

从第三章的原理图中提取出此结构的基本单元，如图 3.1：

图 3.1 基本单元

工作过程分为两部分：预充电和电荷重新分配。三个 MOS 晶体管开关分别处于三种不同的工作状态， $Q_{11}$  导通向高电位充电， $Q_{12}$  导通向低电位放电， $Q_{13}$  导通两个相邻电容电荷重分配，实际设计电路如图 3.2。考虑到：

1) 单个 MOS 晶体管作开关，以 NMOS 为例，栅级电压为 5V，源端的 5V 电压想要传到漏端去，这个过程有两大缺点：

- a. 当输出端的电压达到  $V_{in} - V_{tn}$  时，晶体管进入线性工作区，开关电阻将急剧增大；

- b. 当漏端电压达到  $5 - V_{tn}(V_b)$  时（一般考虑了体效应的  $V_{tn}$  为 1.5V），管子将关断，漏端保持在 3.5V，白白损失了 1.5V，这会降低噪声容限并导致静态功耗。若在其后连一个 CMOS 倒相器，3.5V 的输入电压无法使 PMOS 彻底关断，引起 VDD 和 GND 的直接通路。

因此想到用 NMOS 和 PMOS 并联的传输门作开关。当漏端为 3.5V NMOS 断时，PMOS 还是导通的，源处的 5V 电压能完全传 到漏端，没有电压丢失，双向传输结构降低寄生电阻、电容，用最简单的结构实现快速开关功能。

2) 输入值 b 和时钟 φ 相与后再控制开关会引起额外的不理想状况，所以把 b 和 φ 的控制功能分开实现。

3) 相邻电容会产生耦合，用伪开关放在中间以切断这种效应。

图 3.2 用 Workview Office 软件输入实际设计电路

$M_1, M_2$  由  $b$  控制的 ,  $M_3, M_4$  由 1 控制 ,  $M_4$  视为伪开关 , 中间一路完成预充电操作 ,  $M_5$  由 2 控制 , 与前一位的电荷重分配 ,  $M_6$  由 3 控制 , 与后一位的电荷重分配 , 电容皆等值。

然后导出结构网表 , 转至 hspice 软件 , 在结构网表的基础上设定器件尺寸 , 导入库模型 , 加上激励信号和命令 , 进行模拟仿真。此过程是本次设计的重点 :

1) 模型选择 : 根据要求选用 0.35um SILICIDE (SPQM, 3.3V) LOGIC 工艺的 TSMC BSIM3 ( V3.1 )SPICE MODEL Logs353v.1。注意引用模型时要标明其完整的路径 , 而且必须和模型文件内记载的路径一致 , 否则做 simulate 时会报错 , 所以一旦改变模型文件的位置就要把文件内本身记录着的路径一同改变。

2) MOS 管宽长比设定 :  $w>l$  , 开始先随便取了  $w=30u, l=5u$ , simulate 时报错 , 发现尺寸太大与 0.35u 的工艺不符合 . 一般在放大应用中 ,  $l$  要大于工艺最低限度的 2.5 倍 , 但 MOS 管做开关时 , 没有这个限制 , 可以是最小尺寸 , 所以  $l$  取 0.35u ;  $w$  的选择相对复杂些 , MOS 管开关的导通电阻和  $l/w$  成正比 要想获得小电阻(这关系到开关上电压降和 RC 延迟 ),  $w$  就该大些 , 但寄生电容也将随着  $w$  增大而增大 , 较大寄生电容会导致很多不理想的现象 ,  $w$  又不能太大 , 经过多组数据的尝试 , 最后选定在 3.5u.  $w$  对电路的具体影响将在

第五章实现高速的讨论中详细阐述。若将 M<sub>3</sub> 的 w 调小些，可使寄生电容效应更小些，导通电阻增大不明显。可见，尺寸设定不仅要考虑宽长比，宽、长的具体数值同样重要。

- 3) MOS 管衬底：开始网表中没有写入衬底，这不仅很不规范而且产生了明显的漏电。为了尽量减小漏电，取 NMOS 的衬底为地，PMOS 的衬底为 VDD，使衬底和漏源间的 PN 结处于反偏，漏电流最小。

- 4) 电容值的选择：所有电容都是等值的，开始取 0.05pf，结果电荷分配不平均。开关两边的电容实际上是原来设定的等值电容加上开关寄生电容，若等值电容取值太小，寄生电容就占了主导，所以通过增大电容值，可改善这种情况，当 C=0.5pf 时，情况果然好转。但增大电容也有负面影响，具体分析见第五章实现高速的讨论中。

- 5) 时钟频率选择：据上对 MOS 管和电容尺寸的设定，使用 20M 的时钟频率能够较好地实现基本单元的功能，频率升高难度增大不易实现，分析见后。20M 是采样频率，即每个 clock cycle 周期为 50ns 左右，取一个 高电平 15ns, 低电平 2ns，T = 17ns。

以 b=1 为例，网表如下：

```

* Project DA

* Powerview Wirelist Created with Version 6.2

* Inifile :

* Options : -f -d -# -m -x -l da.sp

* Levels :

*

M1n      3     8    15     0    nch   l=0.35u w=3.5u

M1p      15    4     3     9    pch   l=0.35u w=3.5u

M2n      0     4     3     0    nch   l=0.35u w=3.5u

M2p      3     8     0     9    pch   l=0.35u w=3.5u

M3n      1     2     3     0    nch   l=0.5u  w=2u

M3p      3    12     1     9    pch   l=0.5u  w=2u

```

---

```

M4n      1   2   7   0   nch   l=0.35u w=3.5u

M4p      7   12  1   9   pch   l=0.35u w=3.5u

M5n      7   10  11  0   nch   l=0.35u w=3.5u

M5p      11  14  7   9   pch   l=0.35u w=3.5u

M6n      5   6   7   0   nch   l=0.35u w=3.5u

M6p      7   13  5   9   pch   l=0.35u w=3.5u

vvr     15  0   3.3v

vb1     8   0   3.3v

vb1~    4   0   0

vvdd   9   0   3.3v

vclk1    2   0   pulse (0 3.3 5ns .1ns .1ns 15ns 51ns)

vclk1~   12  0   pulse (3.3 0 5ns .1ns .1ns 15ns 51ns)

vclk2    10  0   pulse (0 3.3 22ns .1ns .1ns 15ns 51ns)

vclk2~   14  0   pulse (3.3 0 22ns .1ns .1ns 15ns 51ns)

vclk3    6   0   pulse (0 3.3 39ns .1ns .1ns 15ns 51ns)

vclk3~   13  0   pulse (3.3 0 39ns .1ns .1ns 15ns 51ns)

C1      11  0   0.5PF  ic=1.5v

C2      7   0   0.5PF  ic=0

C3      5   0   0.5PF  ic=0.5v

.tran 0.5ns 56ns 0ns ui c

* DICTIONARY 16

* 1 = 15

* 2 = 3

* 3 = 1

* 4 = 7

```

```

* 5 = 11

* 6 = 5

* B1 = 8

* CLK1~ = 12

* CLK2~ = 14

* CLK3~ = 13

* B1~ = 4

* GND = 0

* VDD = 9

* CLK1 = 2

* CLK2 = 10

* CLK3 = 6

```

```

.lib 'C:\WINNT\Profiles\jhe\Logs353v.l' TT

.END

```

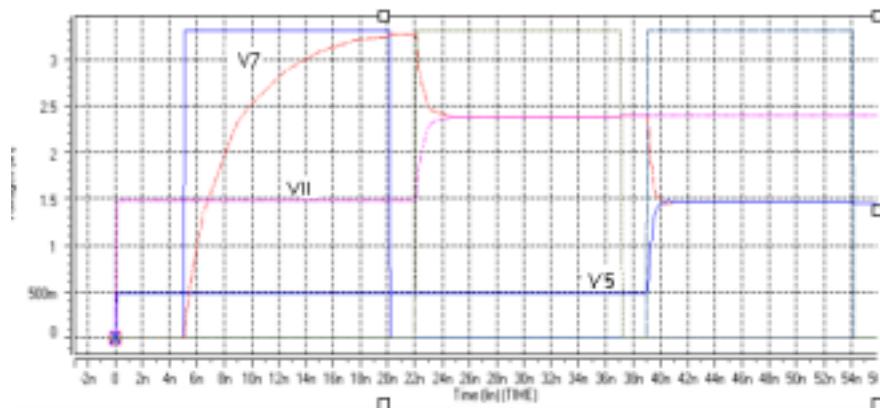

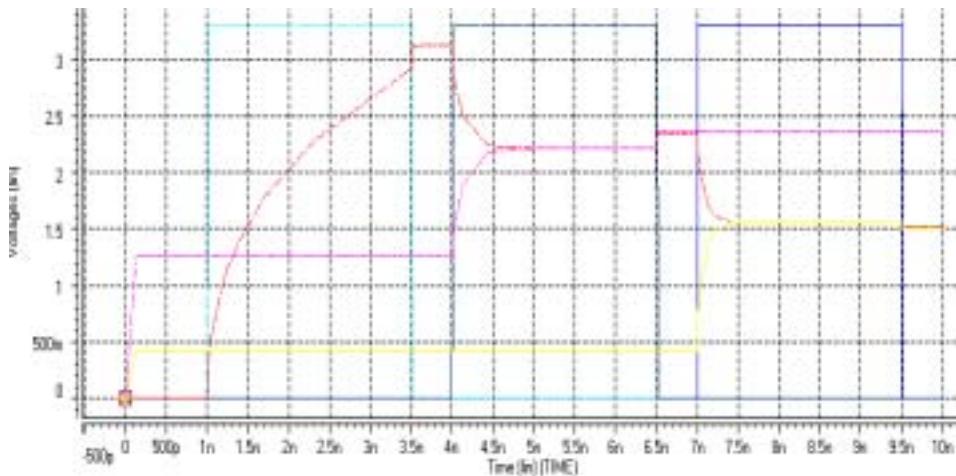

因为只输入一位，目的是想验证基本单元预充电、电荷重分配的功能是否正确，所以时钟只取一个 cycle，前 5ns 为整个过程开始前预留的时间。假定前一位的初始电压是 1.5V，后一位是 0.5V。从 Workview Office 软件中导出的网表，节点编号被打乱，为便于识别，网表中特别将打乱的编号和图形中输入的节点名称对应起来。这里基本上还只考虑理想情况，MOS 管的寄生参数如 AS、AD、PD、PS、NRD、NRS 等都未考虑，以后需进一步改进。基本单元设计的仿真结果如图 3.2：

图 3.2 基本单元设计仿真结果

与电路图结合分析，方波表示 1、2、3 时钟交替，V7 是  $C_2$  中间电容上的电压，V11 是  $C_1$ （前一位）上的，V5 是  $C_3$ （后一位）上的。1 结束时， $C_2$  充至近 3.3V 处，2 变高后  $C_2$ 、 $C_1$  电压平均  $(3.3+1.5)/2 = 2.4V$ ，并在 2 为高时保持此值无漏电，3 变高后  $C_2$ 、 $C_3$  电压平均值为下  $(2.4+0.5)/2 = 1.45V$ ，在 3 为高时保持，见波形图结果较为准确。

## 2.10 位 DAC 的核心设计与结果

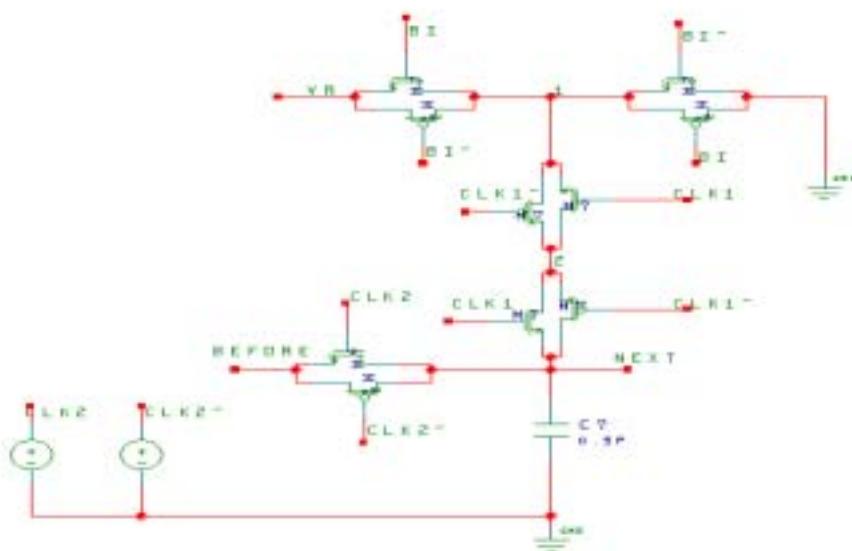

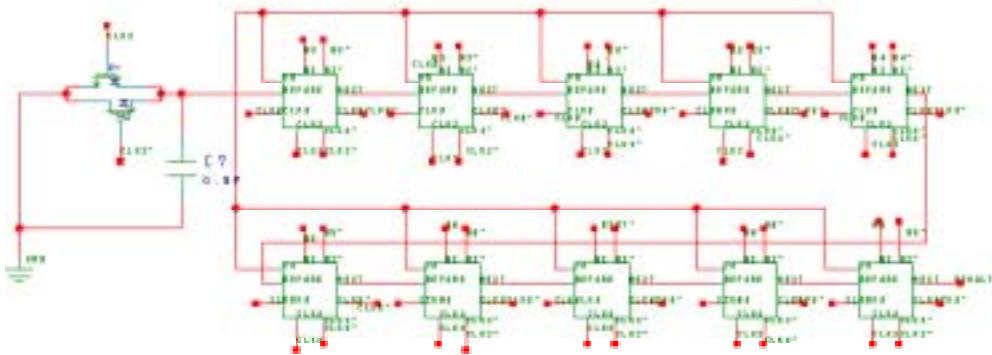

基本单元设计完成后，就可着手将 10 个相同的单元串联起来，配以同步时钟，进行一组 10bit 数据的转换。由于时间所限，没有来得及实现寄存器延缓数据输入功能和流水线结构，在此只是给出了他的核心设计，完成基本功能。（如图 3.4）

上述的基本单元把前后位电容都包含在内，若直接将其作为一个子模块，会有结构上的重叠，现稍做修改，仅包含此位电容以及与前一位相连的传输门开关，BEFORE，NEXT 是与前后模块连的管脚：（如图 3.3）

图 3.3 10 位 DAC 的子模块

10bit 完整图（图 3.4）中最前面的电容和传输门是  $C_0$  和  $Q_{02}$ ，使  $C_0$  的初始电压为 0，后面每一个子模块对应一位输入。最后 RESULT 管脚和  $C_{10}$  相连，这里输出的就是转换结果。同样导出结构网表，转入 hspice，再加上 10 位输入信号，时钟激励和瞬态仿真命令。注意各电容的初始值皆为 0，最后一位值输入后需再经过一个的时间才完成和前一位的电荷分配，所以共需 11T，5ns 预留，瞬态分析时间是  $(17 \times 11 + 5) = 192\text{ns}$ 。

图 3.4 10bit 核心设计电路

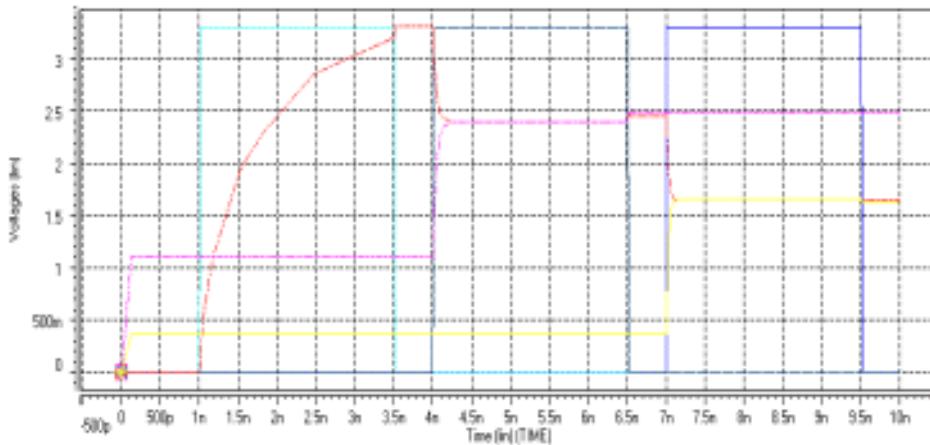

这里引入的都是 hspice 模拟仿真后的原始波形图 ,未加任何修改 ,因为没做数据延缓输入部分 ,每个节点会随着 clock cycle 作周期性充放电 ,我们要重点验证的是随着时钟往前推进 ,数据转换是否也同预想的一样一级一级往后传。

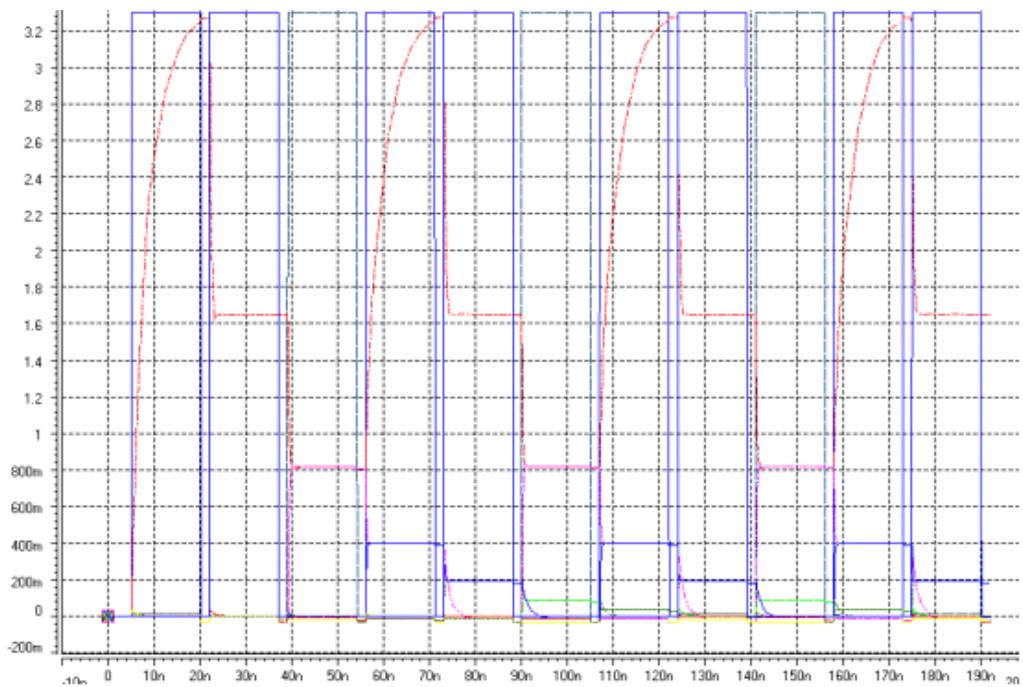

图 3.5 是输入为 1000000000(为和电路图保持一致性 ,从左到右按 b1~b9 顺序)时的情况 ,即 LSB ,由于  $LSB = 3.3/2^{10}=0.0032V$  ,非常小 ,在以 1V 为单位纵坐标的波形图中无法清楚地表示 ,虽然将图形放到最大 ,也只能看到前几位的变化情况 ,不过每经过一位值减小一半的变化趋势却清晰地呈现在我们眼前。

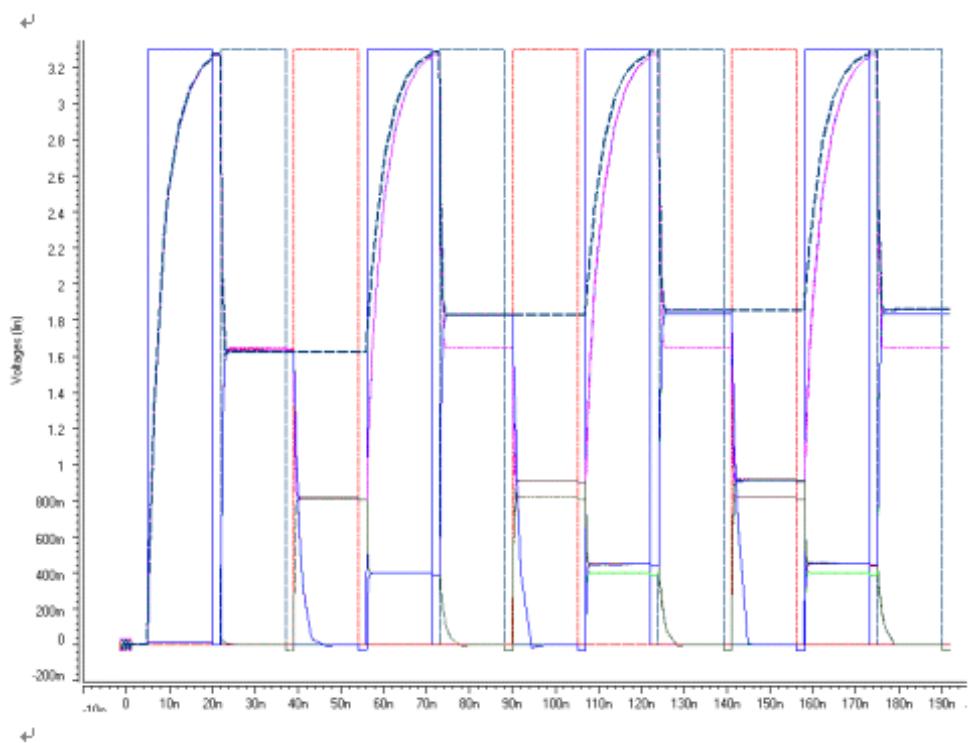

图 3.6 是输入为 0000000001 的情况 ,即  $MSB = 3.3/2^1=1.65V$  ,  $b_{10}=1$  ,  $C_{10}$  在每个 1 时充电 , 2 时和  $C_9$ (电荷为 0)平均分配电荷 ,电压降为一半 , 3 时保持此电压不变。其他节点始终为 0。

图 3.7 为输入 1001001001 情况 ,理想结果应为  $3.3/2^{10}+3.3/2^7+3.3/2^4+3.3/2^1 = 1.885V$  ,从波形图中测量得实际为 1.87V。虽然仍有误差 ,但结果相近可以接受。 $C_1$  充高 , 经过  $C_2$  平均分一半 , 经过  $C_3$  又分一半 , 同时  $C_4$  也被充高 , 然后  $C_3$  上的电荷与  $C_4$  上的平均分 , 所得电荷经过  $C_5$  分一半 , 根据每位输入值类推 , 就得转换结果。

图 3.5 输入为 1000000000 时 hspice 模拟仿真图

图 3.6 输入为 0000000001 时 hspice 模拟仿真图

图 3.7 输入为 1001001001 时 hspice 模拟仿真图

## 第四章 设计讨论

### 1. 实现高速过程中的问题

如将时钟频率提高，设计会复杂得多，关键是对充放电速度的要求提高了，此一条就使原先的设计无法有效工作，低频时掩盖掉的很多不理想因素都凸现了出来。从  $R_{switch}$  和  $C$ （包括寄生电容简称  $C_{\text{寄}}$  与电路中开关相连的等值电容简称  $C_{\text{等}}$ ）入手考虑。

- a. 对  $R_{switch}$ ：他直接关系到预充电能否达到参考源的值 3.3V。一方面， $R_{switch}$  越大，充放电延迟时间越大，高频时导致充电不够；一方面， $R_{switch}$  越大，开关上的电压降越大，即便充电时间足够，也不能使参考电压源的值完全加在电容上，引起误差。所以  $R_{switch}$  要尽量取小他正比于  $1/w^2$ ， $w$  取最小值， $w$  则越大越好。

- b. 对  $C_{\text{寄}}$ ：这是一个很重要的参数，一般来说他越小越好。其一， $C_{\text{寄}}$  如果较大，开关导通时  $C_{\text{寄}}$  上储存的电荷就多，一旦开关关断，这些电荷将向两边的电容涌去，所以在时钟由高变低时，电容上的电荷往往会上冲，极大地引入误差；其二， $C_{\text{寄}}$  若大到能和  $C_{\text{等}}$  比拟甚至超过，那么在分配电荷时他将占主导，引起开关两边实际电容不等，电荷分配不平均；其三， $C_{\text{寄}}$  越大，充放电越慢。已知  $w$  越大， $C_{\text{寄}}$  越大，因此， $w$  越小越好。

- c. 对  $C_{\text{等}}$ ：不同的影响对其要求不同，不能简单地说取大或是取小。第一， $C_{\text{等}}$  只有盖过  $C_{\text{寄}}$ ，占主导地位，才能使开关两边的实际电容相近，保证电荷平均分配，那么  $C_{\text{等}}$  要大；第二， $C_{\text{等}}$  越大，过冲电荷影响越不明显，要求  $C_{\text{等}}$  大；第三， $C_{\text{等}}$  对 RC 延迟的影响很大，为使充放电速度快， $C_{\text{等}}$  就一定要取小，这一点比对  $C_{\text{寄}}$  的要求严格。

根据上述分析，对于各参数的值，尤其是  $w$  和  $C_{\text{等}}$ ，并没有一个明确的要求，陷于顾此失彼的矛盾中，只能随具体应用不同，比较各种性能指标，找到一个权衡的点。这个过程需要反复调试，固定其它参数，将某一参数稍作改动，观察变化，看看与理论分析是否一致，直至达到各性能指标。

在 100M 的条件下进行调试：

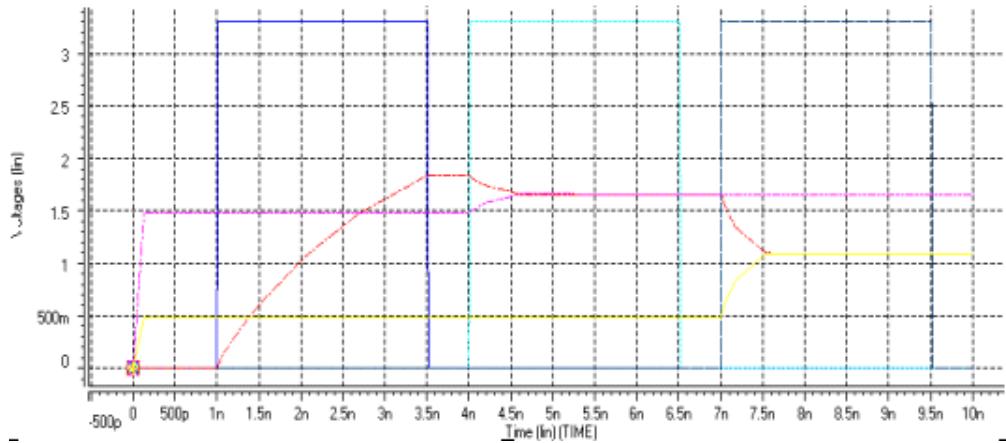

- a. 使用原先 20M 时的设计， $I=0.35\mu A$ ,  $w=3.5\mu s$ ,  $C=0.5\text{pF}$ ，仿真结果如图 4.1：

图 4.1 100M  $I=0.35\mu$ ,  $w=3.5\mu$ ,  $C=0.5\text{pf}$  条件下 hspice 仿真结果

预充电仅到 1.8V 左右，电容太大，RC 延迟时间过长，在 1 结束时来不及充至 3.3V.

b. 据上，减小等值电容的值观察，使  $C=0.05\text{pf}$ ，仿真结果如图 4.2：

图 4.2 100M  $I=0.35\mu$ ,  $w=3.5\mu$ ,  $C=0.05\text{pf}$  条件下 hspice 仿真结果

发现虽然可将电压充高，但电荷分配明显不平均，有少许过冲现象，结果在 1.6V 左右，与理想的 1.45V 有一定差距。将电容再做增大，处于 0.5pf 和 0.05pf 之间，取 0.1pf，仍有充电明显不足的问题，且有少许过冲。下面从另一个角度，改变宽长来试一试，C 取一个相对适中的量，定为 0.1pf。

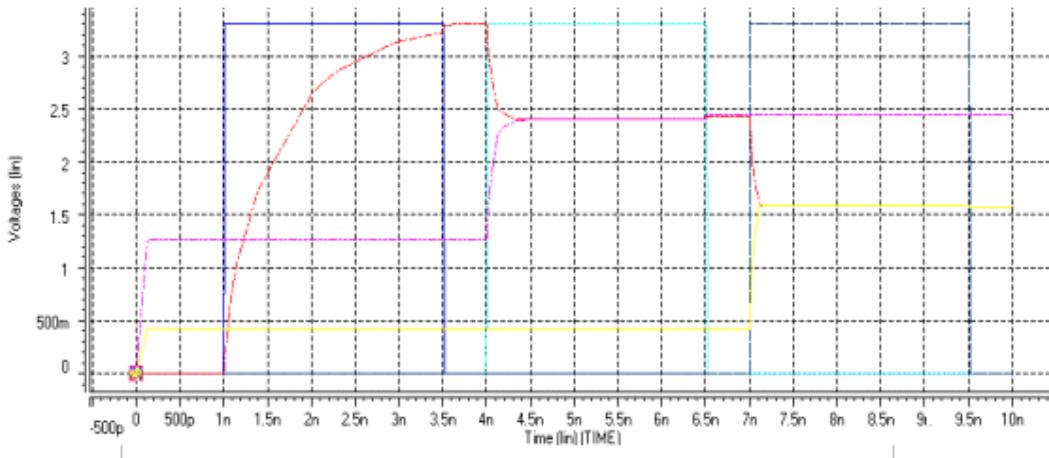

c. 增加长度观察结果，取  $I=1\mu$ ,  $w=3.5\mu$ , 仿真结果如图 4.3：

$I$  增大， $R_{switch}$  增大，一使开关上的电压降升高，二使延迟时间升高，都导致充电达不到参考源的电压值，从波形图中看，还有明显过冲。

图 4.3 100M  $I=1\mu$ ,  $w=3.5\mu$ ,  $C=0.1\text{pf}$  条件下 hspice 仿真结果

d. 为要解决  $C=0.1\text{pf}$  充电不足的问题，减小  $R_{\text{switch}}$  是一种方法。 $I$  恢复到原先最小值  $0.35\mu$ ，并增大  $w$ ，取  $w=7\mu$ ，仿真结果如图 4.4：

图 4.4 100M  $I=0.35\mu$ ,  $w=7\mu$ ,  $C=0.1\text{pf}$  条件下 hspice 仿真结果

$C_{\text{寄}}$  随着  $w$  的增大而增大，其上储存的电荷一多，时钟关断时向两边电容分配的电荷越多，过冲越大。同时  $C_{\text{寄}}$  在  $C_{\text{总}}$  中所占的比重变大，开关两边实际电容不等，电荷分配更不平均，转换结果如图所示。再做进一步调试， $w$  取  $5\mu$ ，过冲和电荷分配稍有好转，但充电下降，因为  $R_{\text{switch}}$  变大，考虑降低  $C$ ，过冲和电荷分配不均又凸现出来。如此反复，顾此却又失彼，想要找到一个 tradeoff 的点，需要进一步探索。

## 2. 非理想效应对转换精度的影响

虽然从理论上说此电路可以很好地实现数字和模拟量的转换，但实际制作的过程中会有很多额外的效应来影响电路的转换精度，主要有以下几个：

a. 电容间的不匹配 (capacitor mismatch)，这是精度不高的主要原因，导致电容不匹配的因素有：

- 1) 不匹配的边缘比例 (mismatched perimeter ratios)

- 2) 单位电容光刻的临近效应 (proximity effects in unit capacitor photolithography)

- 3) 不匹配的长范围的边缘电容 (mismatched long range fringe capacitance)

- 4) 不匹配的互连电容 (mismatched interconnect capacitance)

有几种补偿方法能解决 2bit DAC 电容不匹配的缺陷，引用过来，较有参考价值。（详述请见 3）

b. 由于重叠电容导致的时钟反馈 CFT (clock feedthrough), CFT 引起的失真可通过降低电容耦合减小，另外也能通过缩小开关晶体管尺寸降低寄生电容来达到。

c. 隧道电荷 (channel charges)。

d. 版图级：为了使器件能够尽量靠得紧，将使测试电路外置，电容做成长方形以适应不同的空间。电容靠近还会引起电容耦合，这时中间插 dummy capacitor 来切断耦合，此点设计中已经考虑到。

e. 由于只有一个很小的寄生电容在输入端，时钟反馈使得输入端点在输出端的驱动下产生一个很大的电压跳动，时钟反馈电荷（即此电压跳动的大小）由信号电压的大小决定。要克服这种效应，就需在最后一个开关切断之前就把输出信号取样出来。

## 3. 对电荷不匹配的改进

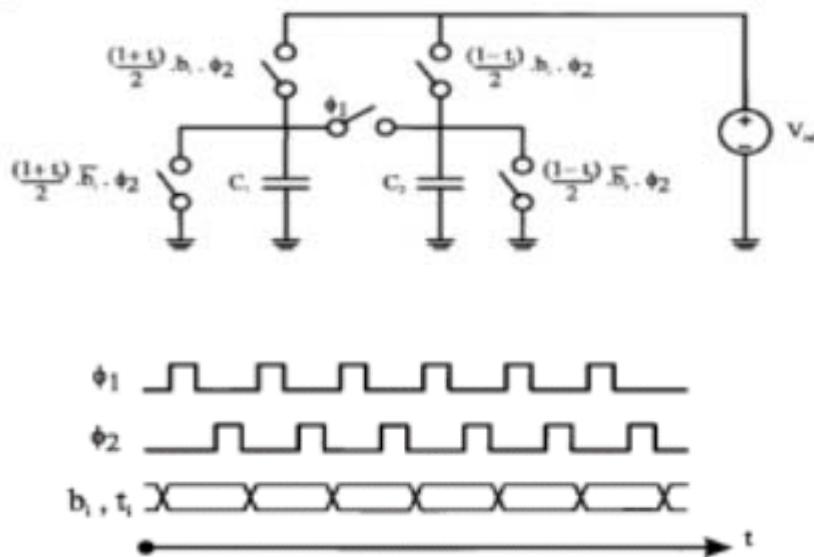

对于一个两位的开关电容 DAC，有一种方法能限制电容不匹配效应，包括两步，首先，使用补偿开关，这对很多输入已经有效，对那些少数此步无效的，再在此基础上，把输入数据分解成两部分，分别输入受电容不匹配的影响远小于直接输入时的情况，最后把两个输出值相加。（使用补偿开关的电路如图 4.5）

这与我们所研究的结构相似，时钟分为预充电相位 1 和电荷重分配相位 2，不同点在于他的工作可有两种模式，以  $C_1$  为预充电电容，将电荷重分配到  $C_2$  上去，称为模式 I，或者相反，称为模式 II。

图 4.5 使用补偿开关电路

定义不匹配因子：

$$\varepsilon = \frac{C_2 - C_1}{C_2 + C_1}$$

用 \$t\_i\$ 表示第 \$i\$ 位的工作模式，\$t\_i=1\$ 表工作在模式 I，\$t\_i=-1\$ 表工作在模式 II。n 位输入的输出值为：

$$\frac{V_{out}(x, t)}{V_{ref}} = \sum_{i=0}^{n-1} 2^{i-n} b_i \frac{(1-t_i\varepsilon)}{(1+t_i\varepsilon)} \prod_{k=i}^{n-1} (1+t_k\varepsilon)$$

与理想值的值的差可用下述函数表示：

$$F_{(n)}(x, t) = \varepsilon V_{ref} \sum_{i=0}^{n-1} b_i 2^{(i-n)} \left( -t_i + \sum_{j=i+1}^{n-1} t_j \right)$$

可见，通过选择 \$t\_i\$，能使误差值最小，我们就把此 \$t\_i\$ 序列称为最佳转换序列。输入值 \$y\$ 可写成 \$y=x\_1+x\_2\$，对两个 \$x\_i\$，都用各自的最佳转换序列分别转换。然后将两模拟量相加。以 2bi \$t\$ 为例，输入有 0. 1. 2. 3 四种可能，由误差函数得：

$$F_{(2)}(0) = 0;$$

$$F_{(2)}(1, t) = (-t_0 + t_1) V_{ref} / 4, \quad t_0=t_1 \text{ 时误差是 } 0;$$

$$F_{(2)}(2, t) = 2(-t_1) V_{ref} / 4, \quad \text{不能限制误差};$$

$$F_{(2)}(3, t) = (-t_0 - t_1) V_{ref} / 4, \quad t_0=-t_1 \text{ 时误差是 } 0;$$

输入是 0、1、3 时，误差可以被限制，若输入为 2，写成 2=1+1，两 1 分别进行，那么误差

同样不存在了。

针对  $n=2N$  精度，需要进一步讨论：a. 哪一些  $x_i$  输入可以经过补偿屏蔽误差；b. 一个具体的输入量  $y$  如何实施最佳分割。这些都有具体规律和演算法则，操作起来步骤清晰，很有实用价值。这里不再做详细论述，只是提供一个可能解决电容不匹配瓶颈问题的思路，希望能对我们的设计有用。

#### 4. 不足与计划

对这种新型 DAC 结构的研究与设计，这次只是刚刚开了头，实现了最核心的功能而已，还有很多功能、性能需要改进，下面列出几个主要方面：

- 1) 用 D 触发器构成寄存器，10bit 数据并非同时输入，要有不同步的延缓输入过程。

- 2) 流水线结构的实现。

- 3) 突破现有的频率，向高频冲刺，这是难点，也是关键。

- 4) 解决电容不匹配问题。

- 5) 开关是一个很复杂的系统，如在充电过程中，MOS 管就会从线性区向饱和区过渡，等等。

进一步研究开关，提高开关速度，包括传输门模型，导通电阻，寄生电容等，具体量化深入分析。

- 6) MOS 管的寄生参数如 AS, AD, PS, PD, NRS, NRD 在 hspice 网表里都未考虑，真正实现设计时，这些因素不能忽略。

- 7) 输门上的控制信号现在都假设为理想的，如 clk 和 clk 非信号同时到达，且完全反相，若用反相器实现反相时钟信号，反向输入数字量，由于器件延迟，会使传输门在该关断的时候没有彻底关断，开关性能不理想。

- 8) 静动态参数的测试。

以上这些都是还存在的严重不足，也是下阶段研究设计的重点，可见，还需做更深入。细致地研究与探索。用 hspice 模拟仿真成功后，在 Cadence 软件上画出版图，并仿真，最后申请流片。

## 结 束 语

毕业设计终于在经历了两个多月的奋战之后接近了尾声，心里既有一种如释重负的感觉又有些许失落，或许身处其中时，除了刚接到项目时的踌躇满志和结果在很多次反复调试之后如预想般呈现在我眼前时的兴奋之外，更多的还是一次次尝试都失败无法突破的迷茫与焦躁，但现在回首看看，我想说，毕设的日子不仅是人生一份宝贵的财富，也具有里程碑意义，我将永远难忘。

这种以开关电容，预充电加电荷分配为基本原理的流水线结构数模转换器与传统电流、电阻、电容型 DAC 有较大区别，若能解决速度和电容匹配等关键问题，对 DAC 领域是有突破性意义的。在毕设的过程中，我对此项目做了全面的了解与分析，实现了核心功能，也对难点与不足进行了细致的讨论。更重要的是，这次研究学习是我走进模电设计的引路者，懂得在模电设计中不能随心所欲改变参数而该从原理出发，耐心细致反复调试，这种动一辄而触全身，寻找权衡点的玄机与奥妙也给我带来了很大的兴趣与快乐。当然，还有很多深入艰巨的工作等待着我，“革命尚未成功，同志仍需努力”，与其说是结束，我更愿意把他当成是一个真正的新生活的开始。

也许是因为毕设的意义不凡，也许是因为第一次写论文所以也就格外珍视。想把他作为我二十多年人生旅程中一件精心雕琢的作品，献给我的亲人、老师、学长和朋友们，希望能是一份满意的答卷。

## 参考文献

- [1] FONG-JIM WANG and SIMON LAW, " A Quasi -Passi ve CMOS D/A Converter , " IEEE, Solid –State Circuit , vol . 24, no. 6, pp. 1752-1755, Dec. 1989.

- [2] Ahmadreza Rofougaran, Glenn Chang, Jacob J. Real , James Y. -C. Chang, Maryam Rofougaran, Paul J. Chang, Masoud Djafari , M. -K. Ku, Edward W. Roth, Asad A. Abidi , and Henry Samueli , " A Single-Chip 900-MHz S-pread-Spectrum Wireless Transceiver in 1-um CMOS-----Part I: Architecture and Transmitter Design---B. D/A Converter , " IEEE, Solid-State Circuit , vol . 33, no. 4, pp. 518-520, Apr. 1998

- [3] P. Rombouts, L. Weyten, J. Raman, and S. Audenaert, " Capacitor Mismatch Compensation for the Quasi -Passive Switched-Capacitor DAC , " IEEE, Transactions On Circuits and Systems, vol . 45, no. 1, pp. 68-71, Jan. 1998

- [4] Behzad Razavi , " Principles of Data Conversion system design , " IEEE Press

## 致 谢

首先感谢我的导师闵昊教授，是他引领我选择了正确的方向，鼓励我走进模电神奇的世界。他在本领域的建树令我钦佩，他的博学多才，机智敏锐，思考分析问题的方法，对新事物的把握以及对信念的坚持与追求都对我今后的发展有很大的触动和启发。

其次感谢我的师兄唐长文博士，他悉心的点拨与引导，严谨的治学态度，广泛的涉猎面，耐心负责的风范和真诚求实的为人，令我在学识与做人方面均获益良多，也大大提高了我对本专业的认识和兴趣。

然后我想向张洋、张洁、杨雪飞、徐科、王杨、杨励，孙慧等师兄师姐致以最诚挚的谢意，是你们的热心帮助与指导，使我的工作得以顺利进行。整个实验室良好的学习和讨论氛围，也为我创造了一个相当良好的学习研究环境，使我今后的学习生活有了很好的开端。

最后，感谢我的父母和家人，是你们二十多年的关爱与养育，才有了我的今天，最想把这本册子献给你们，作为女儿一点小小的心意。

在此，衷心的感谢曾经给予过我关心和帮助的人们。