文章编号:1004-3365(2002)01-0046-05

# 与工艺无关的 Rail-to-Rail CMOS 运算放大器

唐长文,张 洁,闵

专用集成电路与系统国家重点实验室、上海 200433)

摘 要: 设计了一种与工艺无关的 Rail-to-Rail 运算放大器,它采用一种新型的与工艺无关的恒跨导 Rail-to-Rail 输入级结构,输入级的 P 管对和 N 管对的宽长比不需匹配特定的工艺。同时,还 采用了前馈 AB 类控制的 rail-to-rail 输出级,以保证输出级有大的动态输出范围和较强的驱动负 载的能力。在电源电压为2.7~V时,整个运算放大器在 $0.35~\mu m$  Alcatel 工艺和 $0.6~\mu m$  无锡上华工 艺下模拟,其输入级跨导偏差分别为7%和14%,直流增益分别为87.9 dB 和78.4 dB,单位增益带 宽分别为14 MHz 和9 MHz,相位裕度为67度和75度

关键词: 运算放大器; Rail-to-Rail; 恒跨导; AB 类输出级

中图分类号: TN432: TN722.7+7

文献标识码: A

### A Robust Rail-to-Rail CMOS Operational Amplifier

TANG Zhang-wen, ZHANG Jie, MIN Hao

(State Key Laboratory of ASIC & Systems, Fudan Univ., Shanghai 200433, P. R. China)

A robust rail-to-rail operational amplifier is presented, in which a new robust constant gm rail-to-rail input stage is employed. This new circuit is robust in that it does not require transconductance parameter matching n- and p-channel transistors for specific technology. Meanwhile, a front-feed Class AB control is aslo developed to ensure large dynamic range and strong driving capability. The whole circuit is simulated in 0.35  $\mu$ m Alcatel and 0.6  $\mu$ m Wuxi-Shanghua technology at 2.7 V power supply, respectively. The circuits have achieved a maximum transconductance deviation less than 7 % and 14 %, DC gain of 87.9 dB and 78.4 dB, unit gain bandwidth of 14 MHz and 9 MHz, and a phase margin of 67° and 75°, respectively.

Key words: Operational amplifier; R2R(Rail to Rail); Constant transconductance; Class AB output stage **EEACC:** 2570D; 1220

#### 引 1

集成电路工艺技术的发展,使得 MOS 管的特 征尺寸和电源电压不断下降。对于一个运算放大 器[1],一是要求它的输入和输出仍然有大的动态范 围,二是要求输出级仍然有较强的驱动能力,因此, R2R(Rail-to-Rail)运算放大器就变得尤为重要。

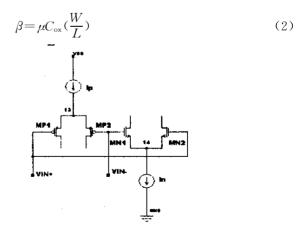

简单的 R2R 运算放大器的输入级[2]如图1所 示。它由一个 PMOS 输入对和一个 NMOS 输入对 并联构成。电路工作可分为三个区:当共模输入电压  $V_{\text{cm}}$ 接近负电源  $V_{\text{SS}}$ 时, NMOS 输入对截止, 只有 PMOS 输入对处于放大状态; 当  $V_{cm}$ 接近正电源  $V_{DD}$ 时,PMOS 输入对截止,只有 NMOS 输入对处于放 大状态: 当共模输入电压处于中间状态时, PMOS 输入对和 NMOS 输入均处于放大状态。图1的输入 级总跨导可由下式表示:

$$g_{\rm mT} = g_{\rm mn} + g_{\rm mp} = \sqrt{\beta_{\rm n} I_{\rm n}} + \sqrt{\beta_{\rm p} I_{\rm p}}$$

(1)

图1 简单的 R2R 输入级

式中, $\beta_n$  和  $\beta_p$  分别是 NMOS 管和 PMOS 管的 跨导参数, $I_n$  和  $I_n$  分别是流经 NMOS 管和 PMOS 管的电流,一般的 R2R 运算放大器要同时满足  $\beta_n$ =  $\beta_{p}$ 、 $I_{n} = I_{p}$ 。可以看到, $V_{cm}$ 在中间状态时,输入级跨导 约变化一倍, $g_{mT}$ 变化将导致运算放大器增益、运算 放大器单位增益带宽都发生变化,这种变化使频率补偿变得困难。为使  $g_{\rm mT}$ 在共模输入电压从  $V_{\rm ss}$ 到  $V_{\rm DD}$ 变化时为一定值,需要设计特定的偏置电路来满

足

$$\sqrt{I_{\rm n}} + \sqrt{I_{\rm p}}$$

为一定值。

我们发现,即使特定的工艺做到了  $g_{mT}$ 在整个 共模输入电压范围内为一定值,在仅改变工艺的情况下,同样结构、同样参数的运算放大器,其性能就 很可能变得面目全非了。因此,在集成电路工艺不断 改进的今天,设计不随工艺变化而变化的运算放大

器或其他模拟电路具有非常重要的意义。

本文从这个思路出发,设计了这样一种新型的与工艺无关的 R2R 运算放大器输入级。它从(1)式右边表达式的整体考虑,通过设计一种独特的控制电路,实现  $V_{\rm cm}$ 从  $V_{\rm SS}$ 到  $V_{\rm DD}$ 变化时, $\sqrt{\beta_{\rm n}I_{\rm n}}+\sqrt{\beta_{\rm p}I_{\rm p}}$ 为一定值。因为它并不要求  $\beta_{\rm n}=\beta_{\rm p}$ ,运算放大器的输入级具有对工艺的自适应性。同时,这个 R2R 运算放大器采用了前馈 AB 类控制的输出级,以保证输

出级有大的动态输出范围和较强的驱动负载能力。

## 2 $\beta_n = \beta_p$ 常跨导输入级

在设计常跨导的输入级时,大多数 R2R 运算放大器 $^{[2,3,4]}$ 都假设  $\beta_n=\beta_p$ ,那么,(1)式可进一步改写为:

$$g_{\rm mT} = g_{\rm mn} + g_{\rm mp} = \sqrt{\beta} \left( \sqrt{I_{\rm n}} + \sqrt{I_{\rm p}} \right) \tag{3}$$

$$\beta = \beta_{\mathrm{n}} = \beta_{\mathrm{p}} = \mu_{\mathrm{n}} C_{\mathrm{ox}} \left( \frac{W_{\mathrm{n}}}{L_{\mathrm{n}}} \right) = \mu_{\mathrm{p}} C_{\mathrm{ox}} \left( \frac{W_{\mathrm{p}}}{L_{\mathrm{p}}} \right) \tag{4}$$

可以看到,只有使 $\sqrt{I_n} + \sqrt{I_p}$ 为常数, $g_{mT}$ 在 $V_{cm}$ 从 $V_{ss}$ 到 $V_{DD}$ 范围内才为一固定值。一倍电流镜控制、三倍电流镜控制、平方根电流控制、电流开关控制等 R2R 运算放大器[5]输入级,就是根据上述原理实现的。同时, $\mu_n$  和 $\mu_p$  是与工艺密切相关的,为了使 $\beta_n = \beta_p$ ,对应于不同的工艺选用的宽长比是不同的,所以,在一种工艺条件下调整好的电路(结构和参数),在另外一种工艺条件下却不能正常工作。即使是同一工艺,由于工艺自身的偏差,也会导致 $\mu_n$ 和 $\mu_p$  偏差 $10\%\sim30\%$ 。

### $\beta_n \neq \beta_n$ 常跨导输入级

$eta_{

m n}=eta_{

m p}$  的假定导致了常跨导输入级对工艺的依赖性。因此,我们摒弃  $eta_{

m n}=eta_{

m p}$  的假定,从 $\sqrt{eta_{

m n}}I_{

m n}+\sqrt{eta_{

m p}}I_{

m p}$  整体考虑,并参考了文献[6]中跨导控制电路。当  $V_{

m cm}$ 接近  $V_{

m SS}$ 时,PMOS 管对通过的最大电流

记为  $I_{\rm pmax}$ ;当  $V_{\rm cm}$ 接近  $V_{\rm DD}$ 时,NMOS 管对通过的最大电流记为  $I_{\rm nmax}$ 。首先设计一个计算电路,计算出给定输入级宽长比时  $I_{\rm pmax}$ 和  $I_{\rm nmax}$ 的值,使得  $\beta_{\rm n}I_{\rm nmax}=\beta_{\rm p}I_{\rm pmax}$ 。然后,设计一个电流控制电路,当  $V_{\rm cm}$ 在  $(V_{\rm DD}+V_{\rm SS})/2$ 附近时,使得 $\sqrt{\beta_{\rm n}I_{\rm n}}+\sqrt{\beta_{\rm p}I_{\rm p}}$ 为一固定值。

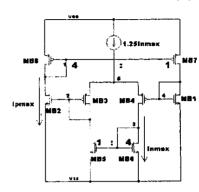

图2 最大电流计算电路

#### 3.1 电流计算电路

式可进一步改写为:

当  $V_{cm}$ 接近  $V_{SS}$ 时, NMOS 管对不导通,  $I_{n,h}$ 0; PMOS 管对完全导通,  $I_{p}$  为  $I_{pmax}$ ; 输入级跨导为:

$$g_{\rm mT} = \sqrt{\beta_{\rm n} I_{\rm n}} + \sqrt{\beta_{\rm p} I_{\rm p}} = \sqrt{\beta_{\rm p} I_{\rm p max}}$$

(5)

当  $V_{cm}$ 接近  $V_{DD}$ 时, PMOS 管对不导通,  $I_{p}$  为0; NMOS 管对完全导通,  $I_{n}$  为  $I_{nmax}$ ; 输入级跨导为:

$$g_{\rm mT} = \sqrt{\beta_{\rm n} I_{\rm n}} + \sqrt{\beta_{\rm p} I_{\rm p}} = \sqrt{\beta_{\rm n} I_{\rm n max}}$$

(6)

为保证  $V_{\rm cm}$ 在  $V_{\rm SS}$ 附近和  $V_{\rm DD}$ 附近时,(5)式与 (6)式相等,则必须  $\beta_{\rm P}I_{\rm pmax}=\beta_{\rm n}I_{\rm nmax}$ 。我们设定  $I_{\rm nmax}$  的值,通过图2所示的最大电流计算电路计算出  $I_{\rm pmax}$  值。NMOS 管  $M_{\rm B1}$ 和  $M_{\rm B2}$ 的宽长比与输入管对  $M_{\rm N1}$ 和  $M_{\rm N2}$ 相同,PMOS 管  $M_{\rm B3}$ 和  $M_{\rm B4}$ 的宽长比与输入管  $M_{\rm P1}$ 和  $M_{\rm P2}$ 相同。 $M_{\rm B8}$ 与  $M_{\rm B7}$ 、 $M_{\rm B6}$ 与  $M_{\rm B5}$ 都是4:1电流 镜,得到下式:

$$V_{\text{SGB3}} + V_{\text{GSB2}} = V_{\text{SGB4}} + V_{\text{GSB1}} \tag{7}$$

$$V_{{ ext{TB}}_3} + \sqrt{rac{2I_{{ ext{B}}_3}}{eta_{{ ext{p}}}}} + V_{{ ext{TB}}_2} + \sqrt{rac{2I_{{ ext{B}}_2}}{eta_{{ ext{n}}}}} =

onumber \ V_{{ ext{TB}}_4} + \sqrt{rac{2I_{{ ext{B}}_4}}{eta_{{ ext{p}}}}} + V_{{ ext{TB}}_1} + \sqrt{rac{2I_{{ ext{B}}_1}}{eta_{{ ext{n}}}}}$$

$V_{\text{TB4}} + \sqrt{\frac{2Y_{\text{B4}}}{\beta_{\text{p}}}} + V_{\text{TB1}} + \sqrt{\frac{2Y_{\text{B1}}}{\beta_{\text{n}}}}$  (8) NMOS 管  $M_{\text{B2}}$ 与  $M_{\text{B1}}$ 的源极都连接到  $V_{\text{SS}}$ ,所

以,阈值电压  $V_{\rm TB2}$ 与  $V_{\rm TB1}$ 可以近似认为是相同的;同样, ${

m PMOS}$  管  $M_{

m B3}$ 与  $M_{

m B4}$ 的源极都连接到节点5,阈值电压  $V_{

m TB3}$ 与  $V_{

m TB4}$ 也可以近似认为是相同的。故(8)

$$\sqrt{\frac{2I_{\rm B3}}{\beta_{\rm p}}} + \sqrt{\frac{2I_{\rm B2}}{\beta_{\rm n}}} = \sqrt{\frac{2I_{\rm B4}}{\beta_{\rm p}}} + \sqrt{\frac{2I_{\rm B1}}{\beta_{\rm n}}}$$

(9)

再由  $I_{\mathrm{B1}}\!=\!rac{1}{4}I_{\mathrm{p\;max}}$ , $I_{\mathrm{B2}}\!=\!I_{\mathrm{pmax}}$ , $I_{\mathrm{B3}}\!=\!rac{1}{4}I_{\mathrm{nmax}}$ , $I_{\mathrm{B4}}\!=\!$

$I_{\text{nmax}}$ ,可得:

$$\beta_{p}I_{pmax} = \beta_{n}I_{nmax} \tag{10}$$

#### 3.2 电流控制电路

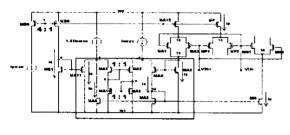

图3是一个电流控制电路,它通过对  $M_{P1}$ 和  $M_{P2}$  PMOS 管对电流的监测,控制通过  $M_{N1}$ 和  $M_{N2}$  NMOS 管对的电流,从而达到常跨导的要求。

图3 电流控制电路

前面所述的最大电流计算电路只计算出了一定的  $I_{nmax}$ 下的  $I_{pmax}$ 值。为了做到  $V_{cm}$ 在  $V_{SS}$ 附近时 PMOS 管对的最大电流是  $I_{pmax}$ 和  $V_{cm}$ 在  $V_{DD}$ 附近时 NMOS 管对的最大电流是  $I_{nmax}$ ,需要采用一个电流控制电路。在图3中, $M_{B8}$ 和  $M_P$  组成的电流镜控制了流过  $M_P$  管的最大电流,当  $M_{B8}$ 和  $M_P$  管都处于强反型时, $M_P$  管的电流  $I_p$  等于通过  $M_{B8}$ 管的电流  $I_{pmax}$ ;当  $M_P$  管渐渐进入线性区, $I_p$  从  $I_{pmax}$ 值逐渐减小。 $M_{A6}$ 、 $M_{A5}$ 和  $M_N$  管的宽长比一样,因此,流过  $M_N$  管的最大电流不会超过流过  $M_{A5}$ 管的电流,而流过  $M_{A5}$ 管的电流与  $M_{A4}$ 管是一样的,不会大于  $I_{nmax}$ 。

$M_{\rm A12}$ 、 $M_{\rm A1}$ 和  $M_{\rm A2}$ 管是  $M_{\rm P}$ 、 $M_{\rm P1}$ 和  $M_{\rm P2}$ 管的一个复本,这样保证了流过  $M_{\rm A3}$ 管的电流完全等于  $I_{\rm p}$ 。图 3实线部分是  $I_{\rm p}$  与  $I_{\rm n}$  转换的控制电路,它保证了当  $I_{\rm p}$  降为 $\frac{1}{4}I_{\rm pmax}$ 时, $I_{\rm n}$  增加到 $\frac{1}{4}I_{\rm nmax}$ 。

$M_{\rm A9}$ 与  $M_{\rm A10}$ 是一个1:1电流镜,流过  $M_{\rm A7}$ 和  $M_{\rm A8}$  管的漏极电流相同,且  $M_{\rm A7}$ 和  $M_{\rm A8}$ 宽长比相同,故  $V_{\rm SG7}$ 等于  $V_{\rm SG8}$ 。这样, $M_{\rm A7}$ 、 $M_{\rm A8}$ 、 $M_{\rm A9}$ 和  $M_{\rm A10}$ 构成了一个电压控制电路,确保节点6和节点7的电压恒相等。 $M_{\rm A11}$ 和  $M_{\rm A4}$ 管的宽长比与输入管  $M_{\rm P1}$ 和  $M_{\rm P2}$ 一样, $M_{\rm A3}$ 和  $M_{\rm B1}$ 管的宽长比与输入管  $M_{\rm N1}$ 和  $M_{\rm N2}$ 一样。从图3中,可以得到下式:

$$V_{6} = V_{\text{SGA}11} + V_{\text{GSB}1} = V_{\text{SGA}4} + V_{\text{GSA}3} = V_{7}$$

$$V_{\text{TA}11} + \sqrt{\frac{2I_{\text{A}11}}{\beta_{\text{p}}}} + V_{\text{TB}1} + \sqrt{\frac{2I_{\text{B}1}}{\beta_{\text{n}}}} =$$

$$V_{\text{TA}4} + \sqrt{\frac{2I_{\text{A}4}}{\beta_{\text{p}}}} + V_{\text{TA}3} + \sqrt{\frac{2I_{\text{A}3}}{\beta_{\text{n}}}}$$

(12)

与最大电流计算电路相类似,NMOS 管  $M_{A3}$ 与  $M_{B1}$ 的源极都连接到  $V_{SS}$ ,阈值电压  $V_{TA3}$ 与  $V_{TB1}$ 可以近似认为是相同的,同样,PMOS 管  $M_{A11}$ 与  $M_{A4}$ 的源极分别连接到等电压节点6和7,阈值电压  $V_{TA11}$ 与

$V_{\mathrm{TA4}}$ 也可以近似认为是相同的。故(12)式可以进一步改写为:

$$\sqrt{\frac{2I_{\text{A}11}}{\beta_{\text{p}}}} + \sqrt{\frac{2I_{\text{B}1}}{\beta_{\text{n}}}} = \sqrt{\frac{2I_{\text{A}4}}{\beta_{\text{p}}}} + \sqrt{\frac{2I_{\text{A}3}}{\beta_{\text{n}}}}$$

(13)

再由  $I_{

m A11} \!=\! I_{

m d}$  (流过  $M_{

m A11}$ 管的电流), $I_{

m B1} \!=\! I_{

m c}$  (流过  $M_{

m B1}$ 管的电流), $I_{

m A4} \!=\! I_{

m n}$ , $I_{

m A3} \!=\! I_{

m p}$ ,(13)式两边都乘

以

$$\frac{1}{2}\sqrt{\beta_{\scriptscriptstyle \rm n}\beta_{\scriptscriptstyle \rm p}}$$

,可得:

$$\sqrt{\beta_{\rm n}I_{\rm c}} + \sqrt{\beta_{\rm p}I_{\rm d}} = \sqrt{\beta_{\rm n}I_{\rm n}} + \sqrt{\beta_{\rm p}I_{\rm p}} \tag{14}$$

$I_{\rm c}$  和  $I_{

m d}$  都是常数,(14)式等式左边是常数,等式右边就是输入级的总跨导  $g_{

m mT}$ 。取  $I_{

m c}\!=\!rac{1}{4}I_{

m nmax}$ 和  $I_{

m d}$

$$= \frac{1}{4}I_{\text{pmax}}$$

,并且由(10)式可得:

$$g_{\text{mT}} = \sqrt{\beta_{\text{n}}I_{\text{n}}} + \sqrt{\beta_{\text{p}}I_{\text{p}}} = \sqrt{\beta_{\text{n}}I_{\text{c}}} + \sqrt{\beta_{\text{p}}I_{\text{d}}} =$$

$$\sqrt{\beta_{n} \times \frac{1}{4} I_{\text{nmax}}} + \sqrt{\beta_{p} \times \frac{1}{4} I_{\text{pmax}}} = \sqrt{\beta_{n} I_{\text{nmax}}} = \sqrt{\beta_{n} I_{\text{nmax}}}$$

(15)

综上所述,在  $\beta_{\rm n}$   $\neq$   $\beta_{\rm p}$  条件下,我们实现了常跨导输入级。

### ■ 前馈 AB 类控制的 R2R 输出级

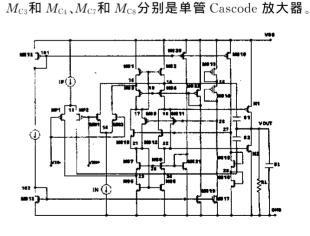

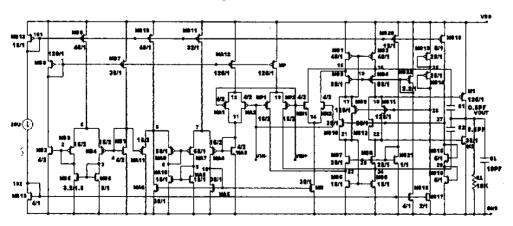

本文的重点在于设计与工艺无关的 R2R 输入级,因此,输出级采用一般的折叠前馈式 AB 类结构<sup>[2,5]</sup>,如图4所示。 $M_1$ 和  $M_2$ 为输出管, $M_{C1}$ 和  $M_{C2}$ 、 $M_{C9}$ 和  $M_{C10}$ 为浮动电压源, $M_{C1}$ 和  $M_{C2}$ 、 $M_{C5}$ 和  $M_{C6}$ 分别是输入 NMOS 管对和 PMOS 管对的有源负载。

图4 折叠前馈式 AB 类输出级

图4的 AB 类控制电路中包括两条回路,一条为 $M_1$ 、 $M_{C11}$ 、 $M_{C14}$ 和  $M_{C13}$ ,另一条为  $M_2$ 、 $M_{C12}$ 、 $M_{C15}$ 和  $M_{C16}$ ,它们控制着输出管的静态电流  $I_q$ 。为了补偿体

效应,分别调节  $M_{C11}$ 和  $M_{C14}$ 、 $M_{C12}$ 和  $M_{C15}$ ,使它们分别具有相同的  $V_{GS}$ ,则  $M_1$ 和  $M_{C13}$ 、 $M_2$ 和  $M_{C16}$ 也分别具有相同的  $V_{GS}$ 。因此,输出级的静态电流可以由下式表示:

$$I_{q} = \frac{\left(\frac{W}{L}\right)_{1}}{\left(\frac{W}{L}\right)_{13}} I_{13} = \frac{\left(\frac{W}{L}\right)_{2}}{\left(\frac{W}{L}\right)_{16}} I_{16}$$

(16)

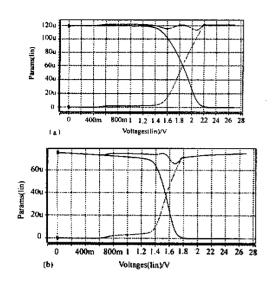

AB 类输出级的电流特性曲线如图5所示。

图5 AB 类输出级电流特性曲线

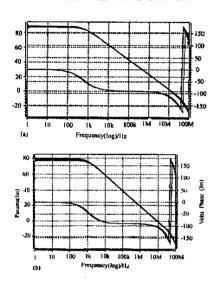

为了提高单位增益带宽和相位余量,我们采用 Cascoded Miller 补偿技术<sup>[2]</sup>。在补偿的过程中,权衡 单位增益带宽和相位余量使补偿电容尽量减小。最 后结果表明,Cascoded Miller 补偿技术能够提高带 宽2倍左右。

### 5 不同工艺条件下的电路实现

整个 R2R 运算放大器首先是在0.35 μm Alca-

tel 工艺下进行模拟的,晶体管的宽长都考虑到与  $0.6~\mu m$  无锡上华工艺兼容。因此在两种工艺条件下,电路结构和参数是完全一样的。整个电路如图  $6~\mu m$  所示,负载为  $10~k\Omega$  电阻与 10~pF 电容并联,电路的模拟性能列于表  $1.6~\mu m$

表1 模拟结果

| 工艺              | 0.35 μm<br>Alcatel 工艺               | 0.6 μm<br>无锡上华工艺                    | 单 位                        |

|-----------------|-------------------------------------|-------------------------------------|----------------------------|

| 输入级跨导           |                                     |                                     | - /                        |

| 误差              | 7                                   | 14                                  | %                          |

| 电源电压            | 2.4~4.5                             | 2.4~4.5                             | V                          |

| 静态功耗            | 2.5                                 | 1.2                                 | mW                         |

| 输出峰值电流          | 6.5                                 | 4.2                                 | mA                         |

| 输入失调电压          | 0.02                                | 0.1                                 | mV                         |

| 等效输入噪声          | 140                                 | 64                                  | ${\rm nV}/\sqrt{{\rm Hz}}$ |

| (f=100  kHz)    |                                     |                                     |                            |

| 共模电压            | $-0.6+V_{\rm SS}\sim$               | $-0.7+V_{\rm ss}\sim$               | V                          |

| 输入范围            | $V_{\rm DD} + 0.5$                  | $V_{\rm DD} + 0.6$                  | V                          |

| 输出电压范围          | $V_{\rm SS} \sim V_{\rm DD} - 0.08$ | $V_{\rm SS} \sim V_{\rm DD} - 0.05$ | V                          |

| 直流增益            | 87.9±0.7                            | 78.4±1.2                            | dB                         |

| 单位增益带宽          | 14±0.8                              | 9.0±0.5                             | MHz                        |

| 相位裕度            | 67±3                                | 75±1                                | 0                          |

| THD( <b>单位</b>  |                                     |                                     |                            |

| 增益反馈            | 2.758e-02                           | 6.853e-03                           | %                          |

| f=1  kHz, 1  V) |                                     |                                     |                            |

| 转换速率            | 37.5                                | 12.5                                | $V/\mu s$                  |

| 建立时间            | 89                                  | 150                                 | ne                         |

| (0.1%,1 V)      | 09                                  | 130                                 | ns                         |

图6 与工艺无关的 R2R 运算放大器电路

在两种不同的工艺下,我们分别比较了输入级跨导和幅频特性,其仿真波形分别如图7和图8所示,

其中,(a)是在 Alcatel 0.35 μm 工艺下模拟的结果,(b)是在无锡上华0.6 μm 工艺下模拟的结果。

图7 输入级跨导曲线图

图8 幅频特性曲线图

### 6 总 结

本文设计了一种与工艺无关的 R2R 运算放大器,它采用了一种新型的与工艺无关的恒跨导 R2R 输入级结构,其输入级的 P 管对和 N 管对的宽长比不需匹配特定的工艺。同时,此运算放大器还采用了

前馈 AB 类控制的 rail-to-rail 输出级来保证输出级有大的动态输出范围和较强的驱动负载的能力。在电源电压为2.7~V~时,整个运算放大器在 $0.35~\mu m$  Alcatel 工艺和  $0.6~\mu m$  无锡上华工艺下模拟,其输入级跨导偏差分别为7%和14%,直流增益单位分别为87.9~dB 和78.4~dB,增益带宽分别为14~MHz 和9~MHz,相位余量为67度和75度。

### 参考文献:

- [1] 李联. MOS 运算放大器——原理、设计及运用[M]. 上海:复旦大学出版社,1988.

- [2] Hogervorst R, Tero J P, Eschauzier R G H, et al. A compact power-efficient 3V CMOS rail-to-rail input/output operational amplifier for VLSI cell libraries [J]. IEEE J Sol Sta Circ, 1994; 29(12): 1505-1512.

- [3] Hogervorst R, Tero J P, Huijsing J H. Compact CMOS constant- $g_m$  rail-to-rail input stage with  $g_m$ -control by an electronic Zener diode[J]. IEEE J Sol Sta Circ,1996;31(7):1035-1040.

- [4] Langen K J, Huijsing J H. Compact low-voltage power-efficient operational amplifier cells for VLSI [J]. IEEE J Sol Sta Circ, 1998; 33(10):1482-1496.

- [5] Hogervorst R, Huijsing J H. Design of low-voltage low-power operational amplifier cells [M]. Kluwer Academic Publishers, Netherlands.

- [6] Sakurai S, Ismail M. Robust design of rail-to-rail CMOS operational amplifiers for a low power supply voltage [J]. IEEE J Sol Sta Circ, 1996; 31(2):146-156.

作者简介: 唐长文(1977—),男(汉族),江西临川人,硕士研究生,1999年毕业于复旦大学电子工程系电子学与信息系统专业,主要研究领域有:数字专用集成电路和模拟单元电路实现、数字信号处理系统设计、数字信号算法 FPGA 结构实

现等,目前正在研究单片多制式数字视频编码器系统。